## **NEUROMATRIX® ARCHITECTURE**

1995 - Module has started development of NeuroMatrix<sup>®</sup> architecture. The architecture is optimized for matrix multiplication algorithms and capable of dynamic precision and performance.

- A specific feature of this architecture is an authentic highperformance vector-matrix coprocessor

- The efficiency of the matrix multiplication operation is close to the theoretical peak

- Low power consumption allows the NeuroMatrix<sup>®</sup> processors to be used in embedded devices for emulation of deep convolutional networks

- 4 generations of NeuroMatrix<sup>®</sup> architecture implemented

- The latest generation (NMC4) featuring hardware support of floating-point computation

nmDL software package (Neuro Matrix for Deep Learning) has been developed to apply the trained deep neural networks on the NeuroMatrix<sup>®</sup> platform (TensorFlow<sup>®</sup> or Caffe<sup>®</sup> libraries).

>15 IP certificates for NeuroMatrix® processor software

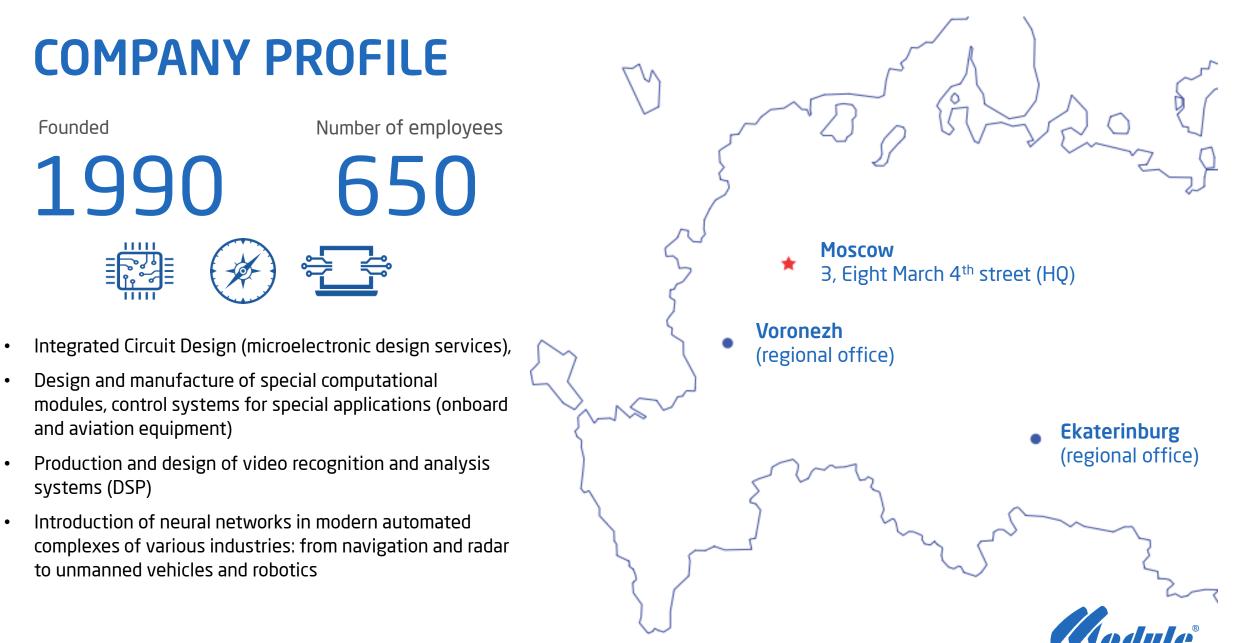

# **Russian NeuroMatrix® processors**

## 1995

- Class 32/64-bit RISC / DSP fixed and floating point

- Highest performance on vector-matrix operations (neural networks, processing of radar, video and signal data)

- Dynamically changing performance to bit ratio

- Patents of the Russian Federation, USA and Korea

#### Main applications

Radar, video processing, neural networks, robotics, GNSS, SDR navigation and communications, astro-orientation, digital television, multimedia, etc.

2019

- IR and video processing

- Navigation

- CDMA и TDMA base station

## NM6406 High performance DSP processor

**NM6406** is a high performance DSP processor designed for real time data flow processing. The architecture is based on the advanced VLIW/SIMD NMC3 core, and consists of a 32/64-bit RISC processor and a 64-bit VECTOR co-processor. The co-processor supports vector/matrix operations with elements of variable bit length (US Pat. 6539368 B1)

## **Features**

| CMOS technology | Package | Clock frequency |

|-----------------|---------|-----------------|

| 90nm            | 416 BGA | 320 MHz         |

|                 |         |                 |

Power supply

1,2 V (core) 3,3 B (I/O buffers)

Performance 320 MIPS (960 MOPS) Temperature range

Power consumption

less than 1,2 W;

- General and real-time information control system: as main SoC

- as interface south bridge

- Ethernet NIC with embedded hypervisor, etc

# **1888BC048**

A versatile 32-bit processor with a wide range of interfaces. Designed for use in embedded equipment.

### Features

CMOS technologyPackageF**28 nm TSMCHSFCBGA-676A**

Processor Architecture **ARM Cortex-A5**

Power supply

Temperature range

-60...+ 85 ° C

0,9V (core)/3.3V (I/O buffers)

Power consumption

- Onboard steering machines

- Input, output, processing, encoding / decoding multimedia information

- Switching and conversion of video streams

# MM7705

#### HD Multimedia Processor

The chip is designed for use as a central processor for devices requiring high performance and high-energy efficiency in computing systems and devices for processing multimedia information.

| CMOS technology | Typical power | Maximum power | Processor Architecture |

|-----------------|---------------|---------------|------------------------|

| 28 nm           | 8 W           | 15 W          | PowerPC v2.05          |

| Processors      |               |               | Power consumption      |

| 2 CPUs (Power   | Max 2,8W      |               |                        |

Hardware video encoder / decoder

1080p high-definition, 60 frames per sec

DDR3 memory, 800-1600Mbps, 32 bits, 2 interfaces with the ability to connect up to 8 GB

## **Neural Networks**

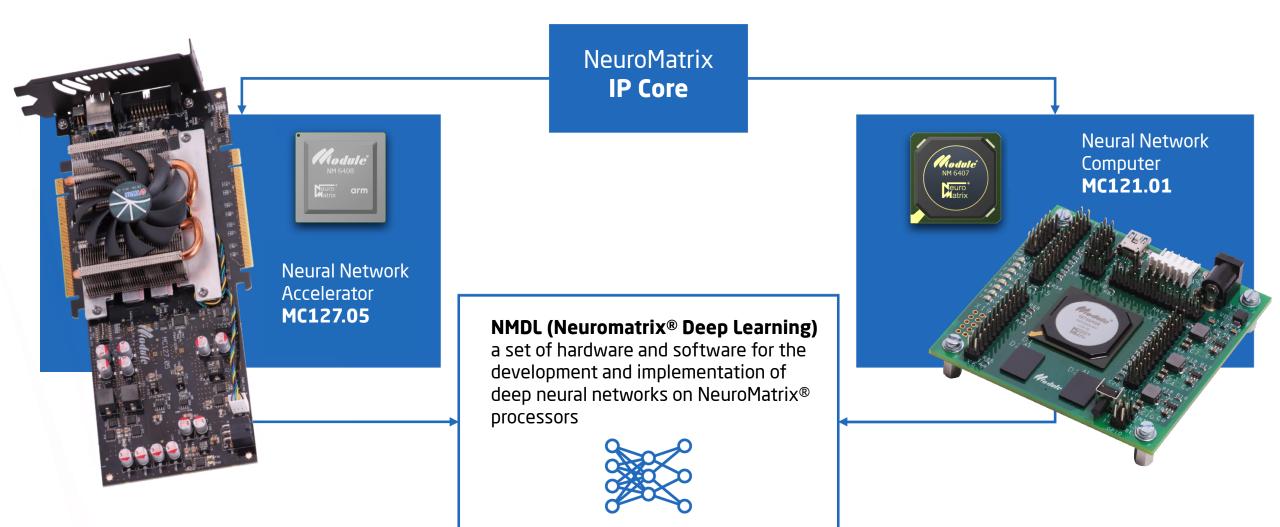

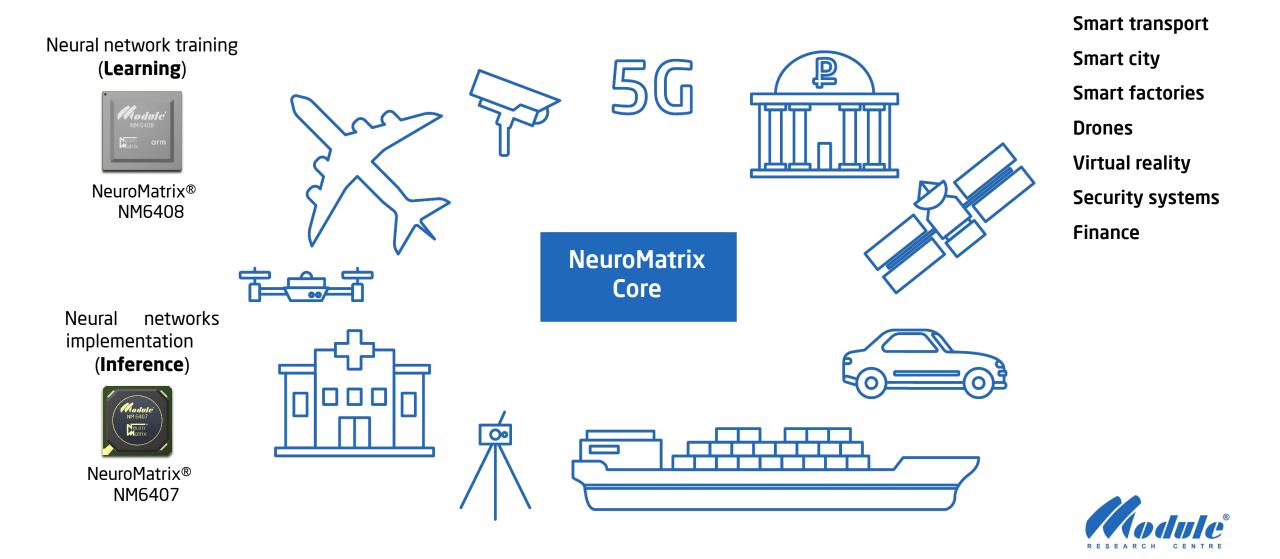

# NeuroMatrix neural network accelerators and computers

NM 6408

Neural network accelerator MC127.05 at NM6408 processor

Embedded MC121.01 computer on the NM6407 processor

**Andule** NM 6407

euro atrix

## Neural Network Computer MC121.01

**MC121.01** is integrated circuit computer designed on the basis of a specialized neural microprocessor **NM6407**.

The module is designed to function as part of a complex, in particular with a PC with USB 2.0 interface. This module is designed to perform a wide class of tasks related to digital signal processing in real time.

Processor clock speed

Speed scalar operations

The total amount of memory

500 MHz

Up to 500 million operations per sec

DDR2 SDRAM 512 MB

Power supply

Power consumption

5 to 12 V

Speed vector operations

up to 12 billion operations per sec with byte operands

2.5 W

- Digital signal processing

- Navigation (transport)

- Radiolocation

- High performance signal switching CDMA and TDMA

# NM6407

High performance neuro-processor for DSP operation

The neuro-processor **NM6407MP** is based on **NeuroMatrix**<sup>®</sup> architecture combining the features of two architectures of VLIW / SIMD processors.

The chip contains two processor cores **NMPUO** and **NMPU1** with a RISC processor and a vector coprocessor for performing vector-matrix operations on integer data of variable length from 1 to 64 bits and floating point vector operations.

## **Features**

|                                | CMOS technology | Memory on a SoC   | Sy            | nchronization frequency |

|--------------------------------|-----------------|-------------------|---------------|-------------------------|

|                                | 65nm            | 16 Mbit           | 5             | 00 MHz                  |

|                                | Voltages        |                   |               | Power consumption       |

| 1.0V (core), 1.8V (DDR2), 3.3V |                 |                   | Typical 2.4 W |                         |

|                                | Performance     | Temperature range |               | Max 7 W                 |

|                                | 16 GFLOPs       | -45 ° C + 85 ° C  |               |                         |

## Neural Network Accelerator MC127.05

The **MC127.05** is a **high performance computing module** with interface capabilities designed to be used as a universal hardware and software platform to receive, process, store and transfer large data in real time. The module can be applied as part of integrated systems to build a wide range of DSP and computer vision systems. The device is based on a heterogeneous high performance NM6408 neuroprocessor, consisting of 16 NM4 cores and five ARM Cortex-A5, five DDR3 controllers and a PCI-E2.0 interface.

## **Features**

- integrated circuit NM6408;

- 5 banks of DDR3 memory, with a total capacity of 5 GB,

- bandwidth up to 32 GB / s;

- PCIe2.0 x4 with a throughput of 4 GB / s;

- Ethernet 100 Mb/s (with EDCL support);

- High-speed communication ports with a capacity of up to 16 GB/s;

- microSD, GPIO (28 pins), JTAG;

- Power consumption 15W;

- Power supply 12V;

- PCIe x16 Form Factor, 2 Slots

#### Applications

- Neural networks and artificial intelligence

- Specialized high-performance complexes

- Digital Signal and Image Processing Systems

- Machine vision systems

- Robotics

- Deep Neural Networks

- SDR navigation and communication

- Video processing

- Radiolocation

- 3D computer vision

- Hybrid high-performance computing systems

# NM6408

#### High performance neuro-processor

The universal neuro-microprocessor is designed for a wide range of tasks, especially in emulation of neural networks and deep learning for special purposes.

**NM6408** is capable of performing complex of operations connected with processing big data streams in real time: digital signal processing (DSP), image processing (recognition), navigation, communication, etc.

## **Features**

CMOS technologyPerformancePower consumption28 nm512 GFLOPs20WPower supplyPackage0,9V (core)/1,8V (I/O buffers)1444 HFCBGA

RESEARCH CENTRE

# NeuroMatrix Neural Network Ecosystem

#### Learning

Neural Net Accelerator MC127.05

NeuroMatrix® NM6408

Supercomputer for neural networks training

Deep Learning Framework

#### Inference

NeuroMatrix® NM6407

Embedded Computer MC 121.01

Tool software(SDK)

NMDL NeuroMatrix® Deep Learning

# Neuro Network Platform Key Elements

# NeuroMatrix Neuro Network Platform

Hardware and

Telemedicine

software systems:

## **Operational Amplifiers**

OAVF1/OAVF2

**OACF1** - one-channel high-speed operational amplifier with voltage feedback.

**OACF2** - two-channel operational amplifier with voltage feedback.

Amplifiers provide high-dynamic accuracy in a wide frequency range and stable operating at gains up to AC = +1. The architecture of the input stages implemented on the bridge differential amplifier provides the **slew rate of the output signal and the cutoff frequency of the maximum power** previously achieved only in broadband amplifiers with current feedback.

#### **Features**

OAs are used in schemes with deep negative feedback, which completely determines the gain / transmission coefficient of the resulting circuit. On the basis of OA it is possible to build many different electronic components.

- Analog-to-digital converters

- Digital-to-analog converters

- Current-voltage converters

- Voltage-current converters

- AC/DC

# **20ACF**

#### Two-channel operational amplifier (OA) with current feedback

It provides good dynamic parameters in a wide range of frequencies and gains, **stably operating on a low-impedance load with gains up to AC = +3 and RH = 10 ohms**. In the OS, the function of turning off each channel is implemented independently, which takes the outputs of the OA to a high-impedance state.

The OA is intended for use in the transceiver path of a high-speed multiplexed data transmission channel (MCPD).

## **Features**

FrequencyMaximum output voltage240 MHz (AC = +4) $7.6 \text{ V} (U = \pm 5 \text{ V})$ The slew rate of amplifierOutput currentTemperature range1030 V/µs500 mA $60 \text{ to } +125 \degree \text{ C}$

- Voltage comparators

- Differential amplifiers and integrators

- Voltage and current stabilizers

- Analog calculators and signal generators

- Analog-to-digital converters

- Digital-to-analog converters

- Current-voltage, voltage-current converters

# **40ACF**

#### Four-channel operational amplifier (OA) with current feedback

It is designed for use in the transceiver path of the high-speed multiplex data channel (MDC). Two op-amp channels are designed for large output currents (up to 500 mA) for the transmitter unit. The other two are smaller (up to 130 mA) and are used for the receiver unit. Transmitter channels operate on a low-impedance load with gains up to AC = +3 and RH = 10 Ohm and have the function of shutting down each channel, independently transforming the OA outputs into a high impedance state. The receiver channels operate at gains up to AC = +1.

## **Features**

Maximum output voltageThe slew rate of amplifier7.6 V (UP =  $\pm$  5 V)1030 V /  $\mu$ s

Frequency **240 MHz (AC = +4)**

Output current **500/130 mA**

Temperature range

60 to +125 ° C

# Navigation

- GLONASS / GPS / GALILEO / COMPASS

- Cellular signal receivers

- Digital broadcasting (DAB)

- Autonomous cars

- Robotics and drones

- Agriculture (precision farming)

- Geodesv

# **GNSS RECEIVER MC149.01**

MC149.01 is a three-frequency receiver. It is designed to build high-precision consumer navigation equipment and provide centimeter-level accuracy in any kind of vehicles and automotive transport systems.

Compatible with library of high precision navigation RTKLib for work with third-party navigation equipment manufacturers.

Centimeter accuracy  $(1\sigma)$

Location Accuracy  $(1\sigma)$

in plan: 1 cm + 1 ppm in height: 1.5 cm + 1 ppm offline mode: 2m SBAS: 0.75m

Simultaneous work in three frequency ranges

#### GLONASS L10F, L20F, L30C, GPS L1 C / A, L2CM, L5

Hardware support

#### BeiDou B1 / B2. Galileo E1 / E5a / E5b. QZSS L1 / L2 20Hz navigation solution temp

Voltage

Power consumption

3.7 - 8.4 V

1.6 - 1.8 W3

- Professional high-precision programmable GNSS solutions

- Navigation programmable receivers

- Telecommunications

- Wide range of digital signal processing for SDR, general purpose computations and control functions

## **BBP2** High performance DSP processor (navigation)

The chip is designed for creating **high-performance measurement modules** that provide reception and processing GNSS GLONASS / GPS / GALILEO signals and SBAS functional addons in navigation equipment. It provides information on the integrity of the navigation field, corrects the information about the exact coordinates of the satellites and the time-frequency parameters of the system.

## **Features**

| CMOS technology | Package   | Performance          |

|-----------------|-----------|----------------------|

| 65nm            | 544 HSBGA | 320 MFLOPS/1040 MIPS |

| Power supply    |           | Power consumption    |

1,2V (core)/3,3V (I/O buffers)

Max 2,8W

## **IP Cores**

RESEARCH CENTRE

# **IP CORES**

Module has designed and tested RTL models of more than 40 IP cores. Some of them:

| No. | IP cores                      |

|-----|-------------------------------|

|     | Multichannel sound controller |

| 2   | CSA 3 descrambler             |

|     | DVB-CI interface controller   |

| 4   | NAND flash controller         |

| 5   | Hardware 3DES accelerator     |

. . . . . .

. . . . . . .

- MPEG-2 Transport Stream Demultiplexer 6

- HDTV video controller

Tested and silicon-proven IP cores are available for order

#### **IP** Core

www.module.ru sales@module.ru +7 495 531 30 80

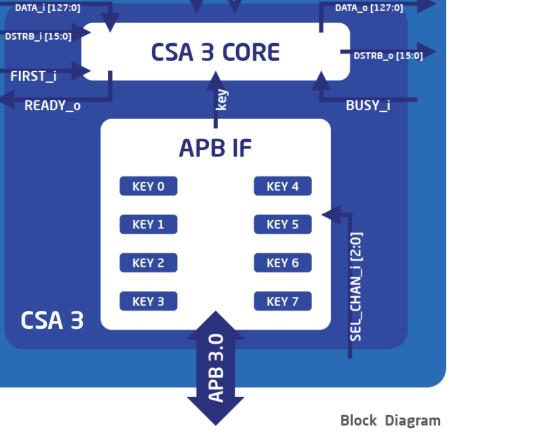

## CSA 3 DESCRAMBLER

#### KEY FEATURES

Full support of DVB CSA 3 Descrambling specification

Flow-through architecture

Up to 4 different transport streams

APB 3.0 interface for programming

About 100 K cells

3.0 interface for proing tion c t 100 K cells trol ar crute compa

#### BENEFITS

Easy to integrate with standard APB interface and simple flow-through data interface

High performance - 5 cycle per byte

Handling up to 4 different transport streams, even and odd keys for each The CSA 3 descrambler IP core is hardware implementation of DVB Common Scrambling Algorithm version 3. It was designed to remove protection from scrambled broadcast data by flow-through decryption of transport stream. It has simple custom interface for data with flow control and APB 3.0 slave interface (backward compatible with APB 2.0) for set keys.

OVERVIEW

The CSA 3 descrambler IP core was designed for handled up to four different transport streams with even and odd keys for each TS. Handling of one 128-bit data word takes about 78 clock cycles (i.e. about 5 clock cycles per 1 byte).

#### APPLICATION

DVB set-top-boxes with conditional access support and multiple tuners

Personal video recorders

Conditional Access Modules

Broadcast equipment

#### **RELATED IP**

Transport Stream Demultiplexer AES Crypto Core DES Crypto Core CSA 2.1 Descrambler

nRS

Ç

Module® and NeuroMatrix® is a registered trade mark of RC Module, JSC. All other names are property of their respective owners. RC Module, JSC, Russia, Moscow, 125190, P/0 166, 3 Eight March 4th Street.

Tel.: +7 499 152 96 98, Fax: +7 499 152 46 61

#### **IP** Core

www.module.ru sales@module.ru +7 495 531 30 80

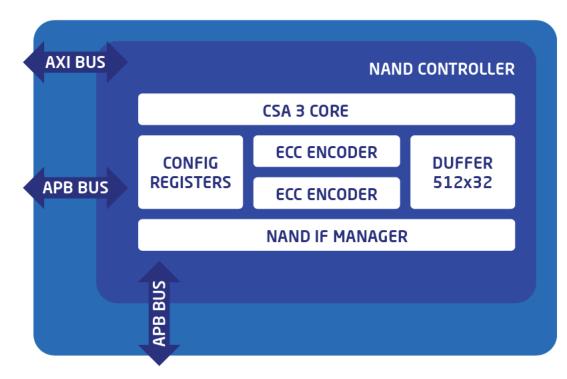

# NAND FLASH CONTROLLER

#### KEY FEATURES

Configurable Flash timing Supports ONFI 2.3 standard command set Only Asynchronous interface supported • Up to 5 address cycles support Internal 2-Kbyte FIFO buffer 8-bit data bus • Hardware ECC support 4, 24 bits correction Support interrupt driven functionality Hardware program/erase protection Supports both SLC and MLC chips Programmable block sizes Programmable page sizes from 0.5KB to 128KB AMBA APB Configuration Interface AMBA AXI 3.0 system interface DMA with big and little endian support

The NAND Flash controller IP core is used as a bridge between external NAND flash memory and master host system. It supports variety of memory manufacturers thanks to hardware ECC support up to 24 errors / 1KB and programmable page size, spare size and erase size. It is compliant to Open NAND Flash Interface (ONFI) 2.3 asynchronous mode supported. Built in DMA engine reduces CPU needs.

Easy to integrate with standard config-

Variety of supported flash chips

uration AMBA APB and AMBA AXI system

#### APPLICATION

OVERVIEW

- DVB set-top-boxes

- USB Mass storage Network Storage

- Media Players

- Mobile Devices

- Portable Devices

- SSD

BENEFIST

interfaces

Area 80000 Gates

**Block Diagram**

IP Core MPEG-2 Transport Stream Demultiplexer www.module.ru sales@module.ru +7 495 531 30 80

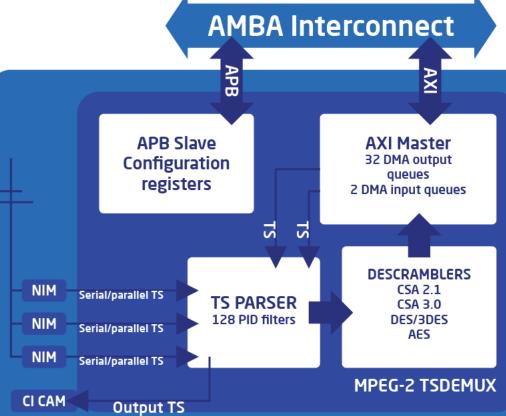

# TSDEMUX

#### KEY FEATURES

• ISO/IEC 13818-1 MPEG-2 complete support Simultaneous processing of 5 MPEG-2 transport streams: 3 external streams from tun¬ers (serial/parallel), 2 stream from system memory Fast hardware PID filtering: 128 hardware PID filters, 32 independent DMA queues for writing filtered data to system memory • Full and partial transport stream recording Pass-through mode Configurable parallel transport stream output interface AMBA 3 AXI Master and APB Slave system integration interfaces Descrambling on TS and PES levels: CSA2.1, CSA3.0, AES, DES/3DES • 80 000 to 380 000 2-input NAND equivalent gates (depends on descramblers configuration), 24Kbit internal RAM

#### BENEFITS

• Easy to integrate with standard AMBA interfaces • Fast hardware PID filtering with 128 filters • Up to 5 independent transport streams simultaneous processing • High performance stream descramblers with multiple key sets and multiple algorithms support

DVB set-top-boxes with conditional access support and multiple tuners

Personal video recorder

- Conditional Access Modules

- Broadcast equipment

#### RELATED IP

AES Crypto Core

DES Crypto Core

CSA 3 Descrambler

CSA 2.1 Descrambler

CRYPTO Accelerator

Block Diagram

Module® and NeuroMatrix® is a registered trade mark of RC Module, JSC. All other names are property of their respective owners. RC Module, JSC, Russia, Moscow, 125190, P/0 166, 3 Eight March 4th Street. Tel.: +7 499 152 96 98, Fax: +7 499 152 46 61 NeuroMatrix<sup>®</sup> NMC3 DSP Core

Interval Timers IP Core

Synchronous Byte Communication I/O Port Controller

Vector Coprocessor IP Core

IP Core Multichannel Audio controller

Smart Card Interface Controller

NAND-Flash Controller IP Core

Transport Stream Demultiplexer IP Core

ARINC818 controller Transmitter and Reciever IP core DVB CSA 3 Descrambler IP core

SpaceWire Channel Controller

NMU Processor System on the NMC3

Test Port Controller IP Core

External Memory Controller

IP Core HDTV Video Controller

Clock-Reset Generator (CRG)

DVB CI Controller

Crypto-accelerator Core

FiberChannel controller IP-core

DVB CSA 2.1 Descrambler IP core

DisplayPort Video Output Device

SPI Controller with DMA

SRAM/NOR Memory Controller with ECC IP Core

AES IP Core

Stream Crypto-accelerator IP Core

Video Capture Unit IP Core

I2S-RX IP-core

SDI-TX IP-core

Audio Output Device of the SPDIF standard

External Interrupt Controller

DMA Controller

Memory Protection Unit

SPDIF-RX IP-core

Video Display Unit IP-core

RESEARCH CENTRE

Cryptograhpic DMA (RMACE) IP-core 3DES IP-core

I2S-TX IP-core

## **TRAFFIC MONITOR®**

# TRAFFIC MONITOR

TrafficMonitor<sup>®</sup> is a family of software products designed for video surveillance of a road section, for real time measuring the traffic flow characteristics, and for transmitting the measured information to a remote traffic control station.

#### TRAFFIC MONITOR PROVIDES THE FOLLOWING FUNCTIONAL TASKS:

Simultaneous analysis of multiple lanes (6 lanes)

# The classification of vehicles

(cars; pick-ups and trucks up to 11 meters; trucks in length from 11 to 14 meters; trucks are longer than 14 meters; buses; motorcycles)

# Automatic detection of events on each band

(stop the vehicle; speed exceeding; opposite direction movement; start and end stage of traffic jams)

#### Measurement of traffic characteristics for each lane separately

(total number of vehicles, passing in a fixed time; number of vehicles of each type; average speed for all vehicles; average speed of vehicles of each type; standard deflection of speed; average

distance between vehicles; average interval time between vehicles; evaluation of lane congestion in percentage)

#### THE SOFTWARE INCLUDES THE FOLLOWING:

#### TMServer

Software network video detector

#### TMKernel

Software video detector module

#### TMControl

TMServer control application

#### **TMAPI**

Application programming interface

# Thank You!

2020 MODULE Research Centre

+7 495 531-30-80

module.ru